# DDR SDRAM

# 4M x 16 Bit x 4 Banks Double Data Rate SDRAM

### Features

- Double-data-rate architecture, two data transfers per clock cycle

- Bi-directional data strobe (DQS)

- Differential clock inputs (CLK and CLK)

- DLL aligns DQ and DQS transition with CLK transition

- Four bank operation

- CAS Latency : 2.5, 3, 4

- Burst Type : Sequential and Interleave

- Burst Length : 2, 4, 8

- All inputs except data & DM are sampled at the rising edge of the system clock (CLK)

- Data I/O transitions on both edges of data strobe (DQS)

- DQS is edge-aligned with data for READs; center-aligned with data for WRITEs

- Data mask (DM) for write masking only

- $V_{DD} = 2.5V \pm 0.2V, V_{DDQ} = 2.5V \pm 0.2V$

- 7.8us refresh interval

- Auto & Self refresh

- 2.5V I/O (SSTL\_2 compatible)

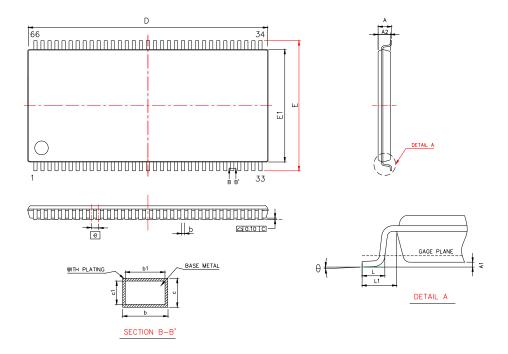

# **Ordering Information**

| Product ID      | Max Freq.       | V <sub>DD</sub> | Package         | Comments |  |

|-----------------|-----------------|-----------------|-----------------|----------|--|

| CT53V161601 -11 | 200MHz (DDR400) |                 | 66 pin TSOPII   |          |  |

| CT53V161601 -12 | 166MHz (DDR333) | 2.5V            | oo piir roof ii |          |  |

| CT53V161601 -18 | 200MHz (DDR400) | 2.50            |                 | Pb-free  |  |

| CT53V161601 -25 | 166MHz (DDR333) |                 | 60 Ball BGA     |          |  |

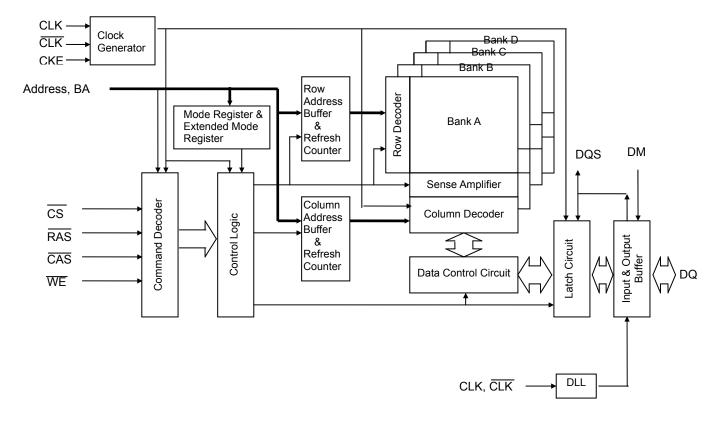

# Functional Block Diagram

# **PIN CONFIGURATION (TOP VIEW)**

(TSOPII 66L, 400milX875mil Body, 0.65mm Pin Pitch)

| 1      |    |    | 1      |

|--------|----|----|--------|

| VDD    | 1  | 66 |        |

|        | 2  | 65 |        |

|        | 3  | 64 |        |

|        | 4  | 63 |        |

|        | 5  | 62 |        |

| Vssq 🗆 | 6  | 61 |        |

|        | 7  | 60 |        |

| DQ4    | 8  | 59 | E DQ11 |

| VDDQ   | 9  | 58 | Vssa   |

|        | 10 | 57 |        |

| DQ6    | 11 | 56 |        |

| Vssa 🗆 | 12 | 55 |        |

| DQ7 🗆  | 13 | 54 |        |

| ИС 🗆   | 14 | 53 | р ис   |

| VDDQ 🗆 | 15 | 52 | 🗅 Vssa |

| LDQS 🗖 | 16 | 51 | DUDQS  |

| ис 🗆   | 17 | 50 | р ис   |

| Vod 🗖  | 18 | 49 | VREF   |

| ис 🗆   | 19 | 48 | 🗅 Vss  |

|        | 20 | 47 |        |

|        | 21 | 46 |        |

| CAS 🗆  | 22 | 45 | р сгк  |

| RAS 🗆  | 23 | 44 | 🗅 СКЕ  |

| cs 🗆   | 24 | 43 | р ис   |

|        | 25 | 42 | D A12  |

| BA₀□   | 26 | 41 | D A11  |

| BA1    | 27 | 40 | P A9   |

| A10/AP | 28 | 39 | 🗆 A8   |

| A0 🗆   | 29 | 38 |        |

| A1 [   | 30 | 37 |        |

| A2 [   | 31 | 36 | A5     |

|        | 32 | 35 |        |

| VDD C  | 33 | 34 | D Vss  |

|        |    |    |        |

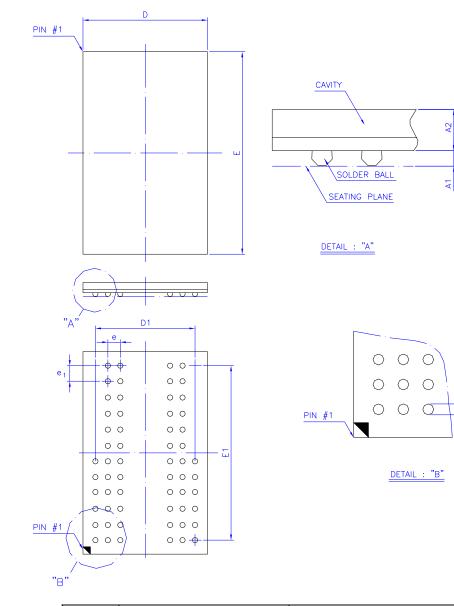

# **BALL CONFIGURATION (TOP VIEW)**

(BGA60, 8mmX13mmX1.0mm Body, 0.8mm Ball Pitch)

# **Pin Description**

| Pin Name            | Function                                                                                                                       | Pin Name         | Function                                                                                                                         |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------|

| A0~A12,<br>BA0, BA1 | Address inputs<br>- Row address A0~A12<br>- Column address A0~A8<br>A10/AP: AUTO Precharge<br>BA0, BA1: Bank selects (4 Banks) | LDM, UDM         | DM is an input mask signal for write data.<br>LDM corresponds to the data on DQ0~DQ7;<br>UDM correspond to the data on DQ8~DQ15. |

| DQ0~DQ15            | Data-in/Data-out                                                                                                               | CLK, CLK         | Clock input                                                                                                                      |

| RAS                 | Row address strobe                                                                                                             | CKE              | Clock enable                                                                                                                     |

| CAS                 | Column address strobe                                                                                                          | CS               | Chip select                                                                                                                      |

| WE                  | Write enable                                                                                                                   | V <sub>DDQ</sub> | Supply Voltage for DQ                                                                                                            |

| V <sub>SS</sub>     | Ground                                                                                                                         | V <sub>SSQ</sub> | Ground for DQ                                                                                                                    |

| V <sub>DD</sub>     | Power                                                                                                                          | V <sub>REF</sub> | Reference Voltage for SSTL_2                                                                                                     |

| LDQS, UDQS          | Bi-directional Data Strobe.<br>LDQS corresponds to the data on DQ0~DQ7;<br>UDQS correspond to the data on DQ8~DQ15.            | NC               | No connection                                                                                                                    |

# **Absolute Maximum Rating**

| Parameter                                                                        | Symbol            | Value                        | Unit |

|----------------------------------------------------------------------------------|-------------------|------------------------------|------|

| Voltage on $V_{\text{DD}}$ & $V_{\text{DDQ}}$ supply relative to $V_{\text{SS}}$ | $V_{DD}, V_{DDQ}$ | -1.0 ~ 3.6                   | V    |

| Voltage on inputs relative to V <sub>SS</sub>                                    | VINPUT            | -1.0 ~ 3.6                   | V    |

| Voltage on I/O pins relative to V <sub>SS</sub>                                  | V <sub>IO</sub>   | -0.5 ~ V <sub>DDQ</sub> +0.5 | V    |

| Operating ambient temperature                                                    | T <sub>A</sub>    | 0 ~ +70                      | °C   |

| Storage temperature                                                              | T <sub>STG</sub>  | -55 ~ +150                   | °C   |

| Power dissipation                                                                | P <sub>D</sub>    | 1                            | W    |

| Short circuit current                                                            | I <sub>OS</sub>   | 50                           | mA   |

Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Note: Functional operation should be restricted to recommend operation condition. Exposure to higher than recommended voltage for extended periods of time could affect device reliability.

# **DC Operation Conditions & Specifications**

# **DC Operation Conditions**

Recommended operating conditions (Voltage reference to  $V_{SS} = 0V$ )

| Parameter                                                                                             | Symbol               | Min                     | Мах                     | Unit | Note |

|-------------------------------------------------------------------------------------------------------|----------------------|-------------------------|-------------------------|------|------|

| Supply voltage                                                                                        | V <sub>DD</sub>      | 2.3                     | 2.7                     | V    |      |

| I/O Supply voltage                                                                                    | V <sub>DDQ</sub>     | 2.3                     | 2.7                     | V    |      |

| I/O Reference voltage                                                                                 | V <sub>REF</sub>     | $0.47*V_{DDQ}$          | 0.51*V <sub>DDQ</sub>   | V    | 1    |

| I/O Termination voltage (system)                                                                      | V <sub>TT</sub>      | V <sub>REF</sub> - 0.04 | V <sub>REF</sub> + 0.04 | V    | 2    |

| Input logic high voltage                                                                              | V <sub>IH</sub> (DC) | V <sub>REF</sub> + 0.15 | V <sub>DDQ</sub> + 0.3  | V    |      |

| Input logic low voltage                                                                               | V <sub>IL</sub> (DC) | -0.3                    | V <sub>REF</sub> - 0.15 | V    |      |

| Input Voltage Level, CLK and CLK inputs                                                               | V <sub>IN</sub> (DC) | -0.3                    | V <sub>DDQ</sub> + 0.3  | V    |      |

| Input Differential Voltage, CLK and CLK inputs                                                        | V <sub>ID</sub> (DC) | 0.36                    | V <sub>DDQ</sub> + 0.6  | V    | 3    |

| V–I Matching: Pullup to Pulldown Current Ratio                                                        | VI (Ratio)           | 0.71                    | 1.4                     | -    | 4    |

| Input leakage current: Any input $0V \le V_{IN} \le V_{DD}$ (All other pins not tested under = $0V$ ) | ١L                   | -2                      | 2                       | μA   |      |

| Output leakage current (DQs are disable; $0V \le V_{OUT} \le V_{DDQ}$ )                               | I <sub>OZ</sub>      | -5                      | 5                       | μA   |      |

### **DC Operation Conditions - continued**

| Parameter                                                                                                                                                          | Symbol          | Min  | Мах | Unit | Note |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------|-----|------|------|

| Output High Current (Full strength driver – Normal) $(V_{OUT} = V_{DDQ}$ -0.373V, min $V_{REF}$ , min $V_{TT}$ )                                                   | I <sub>OH</sub> | -15  |     | mA   | 5, 7 |

| Output Low Current (Full strength driver – Normal) $(V_{OUT} = 0.373V, max V_{REF}, max V_{TT})$                                                                   | I <sub>OL</sub> | +15  |     | mA   | 5, 7 |

| Output High Current (Reduced strength driver –Weak)<br>( $V_{OUT} = V_{DDQ}$ -0.763V, min $V_{REF}$ , min $V_{TT}$ )                                               | I <sub>OH</sub> | -9   |     | mA   | 6    |

| Output Low Current (Reduced strength driver – Weak) $(V_{OUT} = 0.763V, \max V_{REF}, \max V_{TT})$                                                                | I <sub>OL</sub> | +9   |     | mA   | 6    |

| Output High Current (Reduced strength driver –<br>Matched impedance)<br>(V <sub>OUT</sub> = V <sub>DDQ</sub> -1.056V, min V <sub>REF</sub> , min V <sub>TT</sub> ) | I <sub>OH</sub> | -4.5 |     | mA   | 6    |

| Output Low Current (Reduced strength driver –<br>Matched impedance)<br>(V <sub>OUT</sub> = 1.056V, max V <sub>REF</sub> , max V <sub>TT</sub> )                    | I <sub>OL</sub> | +4.5 |     | mA   | 6    |

Notes:

- 1.  $V_{REF}$  is expected to be equal to 0.5\*  $V_{DDQ}$  of the transmitting device, and to track variations in the DC level of the same. Peak-to-peak noise on  $V_{REF}$  may not exceed 2% of the DC value.

- 2. V<sub>TT</sub> is not applied directly to the device. V<sub>TT</sub> is system supply for signal termination resistors, is expected to be set equal to V<sub>REF</sub>, and must track variations in the DC level of V<sub>REF</sub>.

- 3. V<sub>ID</sub> is the magnitude of the difference between the input level on CLK and the input level on  $\overline{\text{CLK}}$ .

- 4. The ratio of the pullup current to the pulldown current is specified for the same temperature and voltage, over the entire temperature and voltage range, for device drain to source voltages from 0.25 V to 1.0 V. For a given output, it represents the maximum difference between pullup and pulldown drivers due to process variation. The full variation in the ratio of the maximum to minimum pullup and pulldown current will not exceed 1.7 for device drain to source voltages from 0.1 to 1.0.

- 5.  $V_{OH}$  = 1.95V,  $V_{OL}$  =0.35V.

- 6.  $V_{OH}$  = 1.9V,  $V_{OL}$  =0.4V.

- 7. The values of  $I_{OH}(DC)$  is based on  $V_{DDQ}$  = 2.3V and  $V_{TT}$  = 1.19V. The values of  $I_{OL}(DC)$  is based on  $V_{DDQ}$  = 2.3V and  $V_{TT}$  = 1.11V.

# **IDD Parameters and Test Conditions**

| Test Condition                                                                                                                                                                                                                                                                                                      | Symbol | Note |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|

| $\begin{array}{l} \textbf{Operating Current (one bank Active - Precharge):} \\ t_{RC} = t_{RC} (min); t_{CK} = t_{CK} (min); DQ, DM, and DQS inputs changing once per clock cycle; \\ Address and control inputs changing once every two clock cycles; \overline{CS} = high between valid commands. \\ \end{array}$ | IDD0   |      |

| <b>Operating Current (one bank Active - Read - Precharge):</b><br>One bank open; BL = 4; $t_{RC} = t_{RC}$ (min); $t_{CK} = t_{CK}$ (min); $l_{OUT} = 0$ mA;<br>Address and control inputs changing once per deselect cycle; $\overline{CS}$ = high between valid commands                                          | IDD1   | 2    |

| Precharge Power-down Standby Current:<br>All banks idle; Power-down mode; $t_{CK} = t_{CK}$ (min); CKE $\leq V_{IL}$ (max); $V_{IN} = V_{REF}$ for DQ, DQS and DM.                                                                                                                                                  | IDD2P  |      |

| Precharge Floating Standby Current: $\overline{CS} \ge V_{IH}(min)$ ; All banks idle; $CKE \ge V_{IH}(min)$ ; $t_{CK} = t_{CK} (min)$ ;Address and other control inputs changing once per clock cycle; $V_{IN} = V_{REF}$ for DQ, DQS, and DM.                                                                      | IDD2F  |      |

| Precharge Quiet Standby Current: $\overline{CS} \ge V_{IH}(min)$ ; All banks idle; $CKE \ge V_{IH}(min)$ ; $t_{CK} = t_{CK} (min)$ ;Address and other control inputs stable at $\ge V_{IH}(min)$ or $\le V_{IL}(max)$ ; $V_{IN} = V_{REF}$ for DQ, DQS, and DM.                                                     | IDD2Q  |      |

| Active Power-down Standby Current:<br>One bank active; Power-down mode; $CKE \le V_{IL}(max)$ ; $t_{CK} = t_{CK}$ (min); $V_{IN} = V_{REF}$ for DQ, DQS, and DM.                                                                                                                                                    | IDD3P  |      |

| Active Standby Current:<br>$\overline{CS} \ge V_{IH}(min)$ ; CKE $\ge V_{IH}(min)$ ; One bank active; $t_{RC} = t_{RAS}$ (max); $t_{CK} = t_{CK}$ (min);<br>DQ, DM, and DQS inputs changing twice per clock cycle;<br>Address and other control inputs changing once per clock cycle.                               | IDD3N  |      |

| <b>Operating Current (burst read):</b><br>BL = 2; Continuous burst reads; One bank active;<br>Address and control inputs changing once per clock cycle; t <sub>CK</sub> = t <sub>CK</sub> (min); I <sub>OUT</sub> = 0mA;<br>50% of data changing on every transfer.                                                 | IDD4R  |      |

| <b>Operating Current (burst write):</b><br>BL = 2; Continuous burst writes; One bank active;<br>Address and control inputs changing once per clock cycle; $t_{CK} = t_{CK}$ (min);<br>DQ, DM, and DQS inputs changing twice per clock cycle; 50% of input data changing at every transfer.                          | IDD4W  |      |

| Auto Refresh Current:<br>t <sub>RC</sub> = t <sub>REC</sub> (min)                                                                                                                                                                                                                                                   | IDD5   |      |

| Self Refresh Current:<br>CKE $\leq$ 0.2V; external clock on; t <sub>CK</sub> = t <sub>CK</sub> (min)                                                                                                                                                                                                                | IDD6   | 1    |

| <b>Operating Current (Four bank operation):</b><br>Four-bank interleaving READs (burst = 4) with auto precharge; $t_{RC} = t_{RC}$ (min); $t_{CK} = t_{CK}$ (min);<br>Address and control inputs change only during ACTIVE, READ, or WRITE commands; $I_{OUT} = 0$ mA.                                              | IDD7   | 2    |

Notes:

1. Enable on-chip refresh and address counters.

2. Random address is changing; 50% of data is changing at every transfer.

### **IDD Specifications**

| Symbol | Vers | sion | Unit |

|--------|------|------|------|

| Symbol | -5   | -6   | Onic |

| IDD0   | 80   | 70   | mA   |

| IDD1   | 110  | 100  | mA   |

| IDD2P  | 4    | 4    | mA   |

| IDD2F  | 30   | 30   | mA   |

| IDD2Q  | 30   | 30   | mA   |

| IDD3P  | 25   | 20   | mA   |

| IDD3N  | 55   | 50   | mA   |

| IDD4R  | 130  | 120  | mA   |

| IDD4W  | 130  | 120  | mA   |

| IDD5   | 140  | 130  | mA   |

| IDD6   | 3    | 3    | mA   |

| IDD7   | 220  | 210  | mA   |

### Input / Output Capacitance

| Parameter                                                                    | Package               | Symbol           | Min | Мах | Delta Cap<br>(max) | Unit | Note    |

|------------------------------------------------------------------------------|-----------------------|------------------|-----|-----|--------------------|------|---------|

| Input capacitance (A0~A12, BA0~BA1,                                          | TSOP C <sub>IN1</sub> | Court            | 2   | 5   | 0.5                | pF   | 1,4     |

| $CKE, \ \overline{CS}, \ \overline{RAS}, \ \overline{CAS}, \ \overline{WE})$ |                       | TBD              | TBD | 0.5 | pF                 | 1,4  |         |

| Input capacitance (CLK, CLK)                                                 | TSOP                  | C <sub>IN2</sub> | 2   | 4   | 0.25               | pF   | 1,4     |

|                                                                              | BGA                   | CIN2             | TBD | TBD |                    | pF   |         |

| Data & DOS input/output capacitance                                          | TSOP                  | Carr             | 1   | 4   | 0.5                | pF   | 1,2,3,4 |

| Data & DQS input/output capacitance                                          | BGA                   | C <sub>OUT</sub> | TBD | TBD | 0.5                | pF   | 1,2,3,4 |

|                                                                              | TSOP                  | C                | 1   | 4   | 0.5                | pF   | 1 2 2 4 |

| Input capacitance (DM)                                                       | BGA                   | CIN3             | TBD | TBD | 0.5                | pF   | 1,2,3,4 |

Notes:

1. These values are guaranteed by design and are tested on a sample basis only.

2. Although DM is an input -only pin, the input capacitance of this pin must model the input capacitance of the DQ and DQS pins. This is required to match signal propagation times of DQ, DQS, and DM in the system.

3. Unused pins are tied to ground.

4. This parameter is sampled.  $V_{DDQ}$  = 2.5V  $\pm$  0.2V,  $V_{DD}$  = 2.5V  $\pm$  0.2V. f=100MHz,  $T_A$  =25°C,  $V_{OUT}(DC)$  =  $V_{DDQ}/2$ ,  $V_{OUT}$  (peak to peak) = 0.2V. DM inputs are grouped with I/O pins - reflecting the fact that they are matched in loading (to facilitate trace matching at the board level).

# **AC Operation Conditions & Timing Specifications**

# AC Operation Conditions

| Parameter                                                     | Symbol               | Min                       | Мах                       | Unit | Note |

|---------------------------------------------------------------|----------------------|---------------------------|---------------------------|------|------|

| Input High (Logic 1) Voltage, DQ, DQS and DM signals          | V <sub>IH</sub> (AC) | V <sub>REF</sub> + 0.31   |                           | V    |      |

| Input Low (Logic 0) Voltage, DQ, DQS and DM signals           | V <sub>IL</sub> (AC) |                           | V <sub>REF</sub> - 0.31   | V    |      |

| Input Differential Voltage, CLK and CLK inputs                | V <sub>ID</sub> (AC) | 0.7                       | $V_{DDQ}$ +0.6            | V    | 1    |

| Input Crossing Point Voltage, CLK and $\overline{CLK}$ inputs | V <sub>IX</sub> (AC) | 0.5*V <sub>DDQ</sub> -0.2 | 0.5*V <sub>DDQ</sub> +0.2 | V    | 2    |

Notes:

- 1.  $V_{ID}$  is the magnitude of the difference between the input level on CLK and the input on  $\overline{CLK}$ .

- 2. The value of  $V_{IX}$  is expected to equal  $0.5^*V_{DDQ}$  of the transmitting device and must track variations in the DC level of the same.

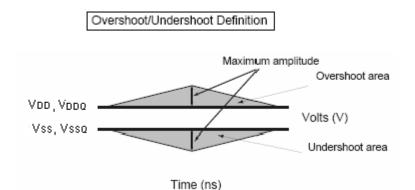

### AC Overshoot / Undershoot Specification

| Parameter                                     | Pin                | Value   | Unit |

|-----------------------------------------------|--------------------|---------|------|

| Falametei                                     | F III              | -5 / -6 | Onit |

| Maximum neek amplitude allowed for everybest  | Address, Control   | 1.5     | V    |

| Maximum peak amplitude allowed for overshoot  | Data, Strobe, Mask | 1.2     | V    |

| Maximum peak amplitude allowed for undershoot | Address, Control   | 1.5     | V    |

|                                               | Data, Strobe, Mask | 1.2     | V    |

|                                               | Address, Control   | 4.5     | V-ns |

| Maximum overshoot area above V <sub>DD</sub>  | Data, Strobe, Mask | 2.4     | V-ns |

| Maximum undershoot area below Ver             | Address, Control   | 4.5     | V-ns |

| Maximum undershoot area below $V_{SS}$        | Data, Strobe, Mask | 2.4     | V-ns |

# AC Timing Parameter & Specifications (Note: 1~6, 9~10)

| _                                          |               |                    | -                                                | 5    | -                                                | 6    |                 |              |

|--------------------------------------------|---------------|--------------------|--------------------------------------------------|------|--------------------------------------------------|------|-----------------|--------------|

| Parame                                     | ter           | Symbol             | min                                              | max  | min                                              | max  | Unit            | Note         |

|                                            | CL2.5         |                    | 5                                                | 12   | 6                                                | 12   |                 |              |

| Clock period                               | CL3           | t <sub>ск</sub>    | 5                                                | 12   | 6                                                | 12   | ns              |              |

|                                            | CL4           |                    | 5                                                | 12   | 6                                                | 12   |                 |              |

| DQ output access time fro                  | m CLK/ CLK    | t <sub>AC</sub>    | -0.7                                             | +0.7 | -0.7                                             | +0.7 | ns              |              |

| CLK high-level width                       |               | t <sub>CH</sub>    | 0.45                                             | 0.55 | 0.45                                             | 0.55 | t <sub>ск</sub> |              |

| CLK low-level width                        |               | t <sub>CL</sub>    | 0.45                                             | 0.55 | 0.45                                             | 0.55 | t <sub>ск</sub> |              |

| DQS output access time fr                  | rom           | t <sub>DQSCK</sub> | -0.6                                             | +0.6 | -0.6                                             | +0.6 | ns              |              |

| Clock to first rising edge of              | f DQS delay   | t <sub>DQSS</sub>  | 0.72                                             | 1.25 | 0.72                                             | 1.25 | t <sub>CK</sub> |              |

| DQ and DM input setup tin                  | ne (to DQS)   | t <sub>DS</sub>    | 0.4                                              |      | 0.4                                              |      | ns              |              |

| DQ and DM input hold time                  | e (to DQS)    | t <sub>DH</sub>    | 0.4                                              |      | 0.4                                              |      | ns              |              |

| DQ and DM input pulse wi input)            | dth (for each | t <sub>DIPW</sub>  | 1.75                                             |      | 1.75                                             |      | ns              | 18           |

| Address and Control input (fast)           | setup time    | t <sub>is</sub>    | 0.6                                              |      | 0.6                                              |      | ns              | 15,<br>17~19 |

| Address and Control input (fast)           | hold time     | t <sub>IH</sub>    | 0.6                                              |      | 0.6                                              |      | ns              | 15,<br>17~19 |

| Address and Control input (slow)           | setup time    | t <sub>IS</sub>    | 0.8                                              |      | 0.8                                              |      | ns              | 16~19        |

| Address and Control input (slow)           | hold time     | t <sub>iH</sub>    | 0.8                                              |      | 0.8                                              |      | ns              | 16~19        |

| Control and Address input (for each input) | pulse width   | t <sub>IPW</sub>   | 2.2                                              |      | 2.2                                              |      | ns              | 18           |

| DQS input high pulse widt                  | h             | t <sub>DQSH</sub>  | 0.35                                             |      | 0.35                                             |      | t <sub>ск</sub> |              |

| DQS input low pulse width                  | l             | t <sub>DQSL</sub>  | 0.35                                             |      | 0.35                                             |      | t <sub>ск</sub> |              |

| DQS falling edge to CLK s                  | etup time     | t <sub>DSS</sub>   | 0.2                                              |      | 0.2                                              |      | t <sub>ск</sub> |              |

| DQS falling edge hold time                 | e from CLK    | t <sub>DSH</sub>   | 0.2                                              |      | 0.2                                              |      | t <sub>ск</sub> |              |

| Data strobe edge to output                 | t data edge   | t <sub>DQSQ</sub>  |                                                  | 0.4  |                                                  | 0.4  | ns              | 22           |

| Data-out high-impedance<br>CLK/ CLK        | time from     | t <sub>HZ</sub>    |                                                  | +0.7 |                                                  | +0.7 | ns              | 11           |

| Data-out low-impedance ti<br>CLK/ CLK      | me from       | t <sub>LZ</sub>    | -0.7                                             | +0.7 | -0.7                                             | +0.7 | ns              | 11           |

| Clock half period                          |               | t <sub>нР</sub>    | t <sub>CL</sub> min<br>or<br>t <sub>CH</sub> min |      | t <sub>CL</sub> min<br>or<br>t <sub>CH</sub> min |      | ns              | 20,21        |

| DQ/DQS output hold time                    | from DQS      | t <sub>QH</sub>    | t <sub>HP</sub> - t <sub>QHS</sub>               |      | t <sub>HP</sub> - t <sub>QHS</sub>               |      | ns              | 21           |

| Data hold skew factor                      |               | t <sub>QHS</sub>   |                                                  | 0.5  |                                                  | 0.5  | ns              |              |

# AC Timing Parameter & Specifications – continued

| Parameter                                               | Symbol             |                                                                                 | 5   | -1                                                                              | 6   | Unit            | Note |

|---------------------------------------------------------|--------------------|---------------------------------------------------------------------------------|-----|---------------------------------------------------------------------------------|-----|-----------------|------|

| Falametei                                               | Symbol             | min                                                                             | max | min                                                                             | max | Onit            | Note |

| Active to Precharge command                             | t <sub>RAS</sub>   | 40                                                                              | 70K | 42                                                                              | 70K | ns              |      |

| Active to Active / Auto Refresh<br>command period       | t <sub>RC</sub>    | 55                                                                              |     | 60                                                                              |     | ns              |      |

| Auto Refresh to Active / Auto Refresh<br>command period | t <sub>RFC</sub>   | 70                                                                              |     | 72                                                                              |     | ns              |      |

| Active to Read, Write delay                             | t <sub>RCD</sub>   | 15                                                                              |     | 18                                                                              |     | ns              |      |

| Precharge command period                                | t <sub>RP</sub>    | 15                                                                              |     | 18                                                                              |     | ns              |      |

| Active to Read with Auto Precharge command              | t <sub>RAP</sub>   | 15                                                                              |     | 18                                                                              |     | ns              |      |

| Active bank A to Active bank B command                  | t <sub>RRD</sub>   | 10                                                                              |     | 12                                                                              |     | ns              |      |

| Write recovery time                                     | t <sub>WR</sub>    | 15                                                                              |     | 15                                                                              |     | ns              |      |

| Write data in to Read command delay                     | t <sub>WTR</sub>   | 2                                                                               |     | 2                                                                               |     | t <sub>ск</sub> |      |

| Average periodic refresh interval                       | t <sub>REFI</sub>  |                                                                                 | 7.8 |                                                                                 | 7.8 | us              | 14   |

| Write preamble                                          | t <sub>WPRE</sub>  | 0.25                                                                            |     | 0.25                                                                            |     | t <sub>ск</sub> |      |

| Write postamble                                         | t <sub>WPST</sub>  | 0.4                                                                             | 0.6 | 0.4                                                                             | 0.6 | t <sub>ск</sub> | 12   |

| Read preamble                                           | t <sub>RPRE</sub>  | 0.9                                                                             | 1.1 | 0.9                                                                             | 1.1 | t <sub>ск</sub> |      |

| Read postamble                                          | t <sub>RPST</sub>  | 0.4                                                                             | 0.6 | 0.4                                                                             | 0.6 | t <sub>ск</sub> |      |

| Clock to DQS write preamble setup time                  | t <sub>WPRES</sub> | 0                                                                               |     | 0                                                                               |     | ns              | 13   |

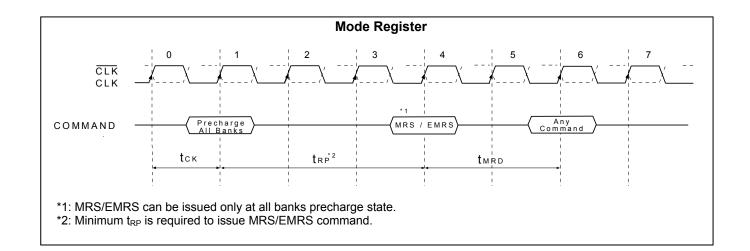

| Mode Register Set command cycle time                    | t <sub>MRD</sub>   | 2                                                                               |     | 2                                                                               |     | t <sub>ск</sub> |      |

| Exit self refresh to Read command                       | t <sub>xsrd</sub>  | 200                                                                             |     | 200                                                                             |     | t <sub>ск</sub> |      |

| Exit self refresh to non-Read command                   | t <sub>xsnr</sub>  | 75                                                                              |     | 75                                                                              |     | ns              |      |

| Auto Precharge write<br>recovery+precharge time         | t <sub>DAL</sub>   | (t <sub>wR</sub> /t <sub>CK</sub> )<br>+<br>(t <sub>RP</sub> /t <sub>CK</sub> ) |     | (t <sub>WR</sub> /t <sub>CK</sub> )<br>+<br>(t <sub>RP</sub> /t <sub>CK</sub> ) |     | tск             | 23   |

Notes:

1. All voltages referenced to  $V_{SS}$ .

2. Tests for AC timing, IDD, and electrical, AC and DC characteristics, may be conducted at nominal reference/supply voltage levels, but the related specifications and device operation are guaranteed for the full voltage range specified.

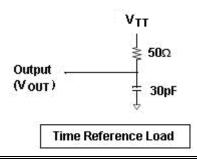

3. The below figure represents the timing reference load used in defining the relevant timing parameters of the part. It is not intended to be either a precise representation of the typical system environment nor a depiction of the actual load presented by a production tester. System designers will use IBIS or other simulation tools to correlate the timing reference load to a system environment. Manufacturers will correlate to their production test conditions (generally a coaxial transmission line terminated at the tester electronics).

- 4. AC timing and IDD tests may use a  $V_{IL}$  to  $V_{IH}$  swing of up to 1.5 V in the test environment, but input timing is still referenced to  $V_{REF}$  (or to the crossing point for CLK/  $\overline{CLK}$ ), and parameter specifications are guaranteed for the specified AC input levels under normal use conditions. The minimum slew rate for the input signals is 1 V/ns in the range between  $V_{IL}(AC)$  and  $V_{IH}(AC)$ .

- 5. The AC and DC input level specifications are as defined in the SSTL\_2 Standard (i.e., the receiver will effectively switch as a result of the signal crossing the AC input level and will remain in that state as long as the signal does not ring back above (below) the DC input LOW (HIGH) level.

- 6. Inputs are not recognized as valid until  $V_{REF}$  stabilizes. Exception: during the period before  $V_{REF}$  stabilizes, CKE  $\leq$  0.2 $V_{DDQ}$  is recognized as LOW.

- 7. Enables on-chip refresh and address counters.

- 8. IDD specifications are tested after the device is properly initialized.

- 9. The CLK/ CLK input reference level (for timing referenced to CLK/ CLK ) is the point at which CLK and CLK cross; the input reference level for signals other than CLK/ CLK , is V<sub>RFF</sub>.

- 10. The output timing reference voltage level is  $V_{TT}$ .

- 11. t<sub>HZ</sub> and t<sub>LZ</sub> transitions occur in the same access time windows as valid data transitions. These parameters are not referenced to a specific voltage level but specify when the device output is no longer driving (t<sub>HZ</sub>), or begins driving (t<sub>LZ</sub>).

- 12. The maximum limit for this parameter is not a device limit. The device will operate with a greater value for this parameter, but system performance (bus turnaround) will degrade accordingly.

- 13. The specific requirement is that DQS be valid (HIGH, LOW, or at some point on a valid transition) on or before this CLK edge. A valid transition is defined as monotonic and meeting the input slew rate specifications of the device. When no writes were previously in progress on the bus, DQS will be transitioning from High- Z to logic LOW. If a previous write was in progress, DQS could be HIGH, LOW, or transitioning from HIGH to LOW at this time, depending on t<sub>DQSS</sub>.

- 14. A maximum of eight AUTO REFRESH commands can be posted to any given DDR SDRAM device.

- 15. For command/address input slew rate  $\geq$  1.0 V/ns

- 16. For command/address input slew rate  $\geq$  0.5 V/ns and < 1.0 V/ns

- 17. For CLK &  $\overline{\text{CLK}}$  slew rate  $\geq$  1.0 V/ns

- 18. These parameters guarantee device timing, but they are not necessarily tested on each device. They may be guaranteed by device design or tester correlation.

- 19. Slew Rate is measured between  $V_{OH}(AC)$  and  $V_{OL}(AC)$ .

- 20. Min ( $t_{CL}$ ,  $t_{CH}$ ) refers to the smaller of the actual clock low time and the actual clock high time as provided to the device (i.e. this value can be greater than the minimum specification limits for  $t_{CL}$  and  $t_{CH}$ ).....For example,  $t_{CL}$  and  $t_{CH}$  are = 50% of the period, less the half period jitter ( $t_{J|T}$ (HP)) of the clock source, and less the half period jitter due to crosstalk ( $t_{J|T}$ (crosstalk)) into the clock traces.

- 21.  $t_{QH} = t_{HP} t_{QHS}$ , where:

$t_{HP}$  = minimum half clock period for any given cycle and is defined by clock high or clock low ( $t_{CH}$ ,  $t_{CL}$ ).  $t_{QHS}$  accounts for 1) The pulse duration distortion of on-chip clock circuits; and 2) The worst case push-out of DQS on one transition followed by the worst case pull-in of DQ on the next transition, both of which are, separately, due to data pin skew and output pattern effects, and p-channel to n-channel variation of the output drivers.

- 22. t<sub>DQSQ</sub> Consists of data pin skew and output pattern effects, and p-channel to n-channel variation of the output drivers for any given cycle.

- 23. For each of the terms above, if not already an integer, round to the next highest integer.

# **Command Truth Table**

| COMMAND                       |                | CKEn-1      | CKEn | CS | RAS |   | WE | DM | BA0,<br>BA1 | A10/AP | A12~A11,<br>A9~A0    | Note               |       |

|-------------------------------|----------------|-------------|------|----|-----|---|----|----|-------------|--------|----------------------|--------------------|-------|

| Register                      | Extended MRS   |             | Н    | Х  | L   | L | L  | L  | Х           |        | OP COD               | DE                 | 1,2   |

| Register                      | Mode Reg       | gister Set  | Н    | Х  | L   | L | L  | L  | Х           |        | OP CODE              |                    | 1,2   |

|                               | Auto R         | efresh      | ц    | Н  |     |   |    | Н  | х           |        | х                    |                    | 3     |

| Refresh                       |                | Entry       | Н    | L  | L   | L | L  | п  | ^           |        | ~                    |                    | 3     |

|                               | Self Refresh   | <b>F</b> :4 |      |    | L   | Н | Н  | Н  | v           |        | V                    |                    | 3     |

|                               |                | Exit        | L    | Н  | Н   | Х | Х  | Х  | Х           |        | Х                    |                    | 3     |

| Bank /                        | Active & Row   | Addr.       | н    | Х  | L   | L | Н  | Н  | Х           | V      | Row                  | Address            |       |

| Read &                        | Auto Precha    | rge Disable |      |    |     |   |    |    |             |        | L                    | Column             | 4     |

| Column<br>Address             | Auto Precha    | arge Enable | Н    | X  | L   | Н | L  | Н  | X           | V      | H Address<br>(A0~A8) | 4                  |       |

| Write &                       | Auto Precha    | rge Disable |      |    |     |   |    |    |             |        | L                    | Column             | 4,8   |

| Column<br>Address Auto Precha |                | arge Enable | Н    | X  | L   | Н | L  | L  | V           | V      | н                    | Address<br>(A0~A8) | 4,6,8 |

| В                             | urst Terminate | ;           | н    | Х  | L   | Н | Н  | L  | Х           |        | Х                    |                    | 7     |

| Dracharga                     | Bank Se        | election    |      | x  |     | 1 | н  | L  | х           | V      | L                    | v                  |       |

| Precharge                     | All Ba         | anks        | Н    | ~  | L   | L | п  | L  | ^           | Х      | н х                  |                    | 5     |

|                               |                | Entry       | н    | L  | Н   | Х | Х  | Х  | х           |        |                      |                    |       |

| Active Power                  | Down Mode      | Enuy        | п    |    | L   | Н | Н  | Н  | ^           |        | Х                    |                    |       |

|                               |                | Exit        | L    | Н  | Х   | Х | Х  | Х  | Х           |        |                      |                    |       |

|                               |                | Entry       | н    | L  | Н   | Х | Х  | Х  | x           |        |                      |                    |       |

| Precharge P                   |                | Linu y      |      |    | L   | Н | Н  | Н  | ^           |        | х                    |                    |       |

| Mode                          |                | Fxit        | L    | н  | Н   | Х | Х  | Х  | x           |        | ^                    |                    |       |

|                               |                |             |      | L  | Н   | Н | Н  |    |             |        |                      |                    |       |

| D                             | eselect (NOP   | )           | н    | x  | Н   | Х | Х  | Х  | x           |        | х                    |                    |       |

| No (                          | Operation (NC  | DP)         |      |    | L   | Н | Н  | Н  |             |        | ~                    |                    |       |

Notes:

1. OP Code: Operand Code. A0~A12 & BA0~BA1: Program keys. (@EMRS/MRS)

- 2. EMRS/MRS can be issued only at all banks precharge state.

- A new command can be issued 2 clock cycles after EMRS or MRS.

- Auto refresh functions are same as the CBR refresh of DRAM. The automatical precharge without row precharge command is meant by "Auto". Auto/self refresh can be issued only at all banks precharge state.

- 4. BA0~BA1: Bank select addresses. If both BA0 and BA1 are "Low" at read, write, row active and precharge, bank A is selected. If BA0 is "High" and BA1 is "Low" at read, write, row active and precharge, bank B is selected. If BA0 is "Low" and BA1 is "High" at read, write, row active and precharge, bank C is selected. If both BA0 and BA1 are "High" at read, write, row active and precharge, bank D is selected.

- 5. If A10/AP is "High" at row precharge, BA0 and BA1 are ignored and all banks are selected.

- During burst write with auto precharge, new read/write command can not be issued. Another bank read/write command can be issued after the end of burst. New row active of the associated bank can be issued at t<sub>RP</sub> after end of burst.

- 7. Burst Terminate command is valid at every burst length.

- 8. DM and Data-in are sampled at the rising and falling edges of the DQS. Data-in byte are masked if the corresponding and coincident DM is "High". (Write DM latency is 0).

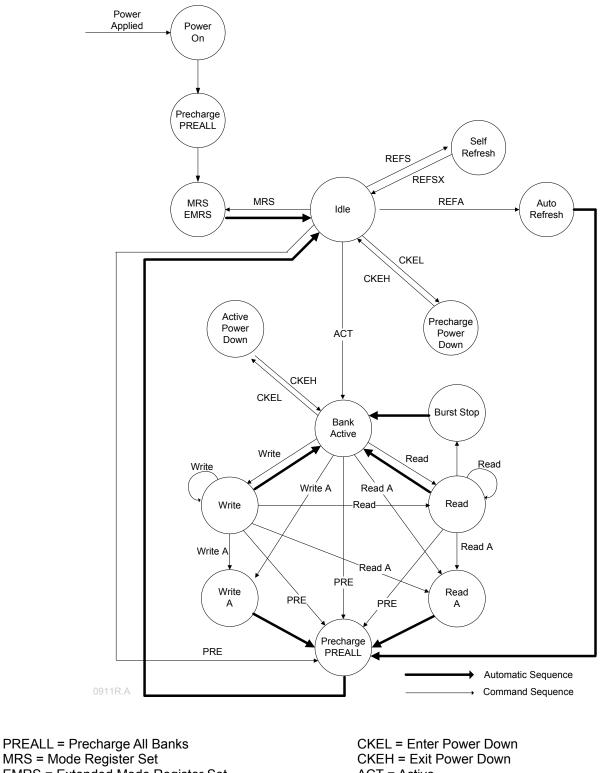

# **Basic Functionality**

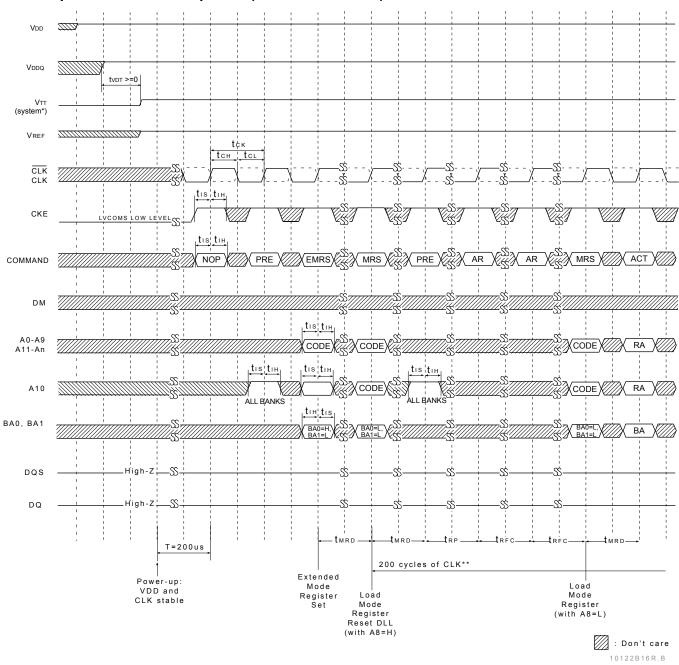

#### Power-Up and Initialization Sequence

DDR SDRAM must be powered up and initialized in a predefined manner. Operational procedures other than those specified may result in undefined operation. No power sequencing is specified during power up and power down given the following criteria:

- V<sub>DD</sub> and V<sub>DDQ</sub> are driven from a single power converter output, AND

- V<sub>TT</sub> is limited to 1.35 V, AND

- V<sub>REF</sub> tracks V<sub>DDQ</sub> /2

- OR, the following relationships must be followed:

- V<sub>DDQ</sub> is driven after or with V<sub>DD</sub> such that V<sub>DDQ</sub> < V<sub>DD</sub> + 0.3 V, AND

- $V_{TT}$  is driven after or with  $V_{DDQ}$  such that  $V_{TT} < V_{DDQ} + 0.3 V$ , AND

- V<sub>REF</sub> is driven after or with V<sub>DDQ</sub> such that V<sub>REF</sub> < V<sub>DDQ</sub> + 0.3 V.

At least one of these two conditions must be met.

Except for CKE, inputs are not recognized as valid until after  $V_{REF}$  is applied. CKE is an SSTL\_2 input, but will detect an LVCMOS LOW level after  $V_{DD}$  is applied. Maintaining an LVCMOS LOW level on CKE during power-up is required to guarantee that the DQ and DQS outputs will be in the High-Z state, where they will remain until driven in normal operation (by a read access).

After all power supply and reference voltages are stable, and the clock is stable, the DDR SDRAM requires a 200 µs delay prior to applying an executable command. Once the 200 µs delay has been satisfied, a DESELECT or NOP command should be applied, and CKE should be brought HIGH.

Following the NOP command, a PRECHARGE ALL command should be applied. Next a MODE REGISTER SET command should be issued for the Extended Mode Register, to enable the DLL, and then a MODE REGISTER SET command should be issued for the Mode Register, to reset the DLL, and to program the operating parameters. 200 clock cycles are required between the DLL reset and any executable command. A PRECHARGE ALL command should be applied, placing the device in the "all banks idle" state.

Once in the idle state, two AUTO refresh cycles must be performed. Additionally, a MODE REGISTER SET command for the Mode Register, with the reset DLL bit deactivated (i.e., to program operating parameters without resetting the DLL) must be performed.

Following these cycles, the DDR SDRAM is ready for normal operation.

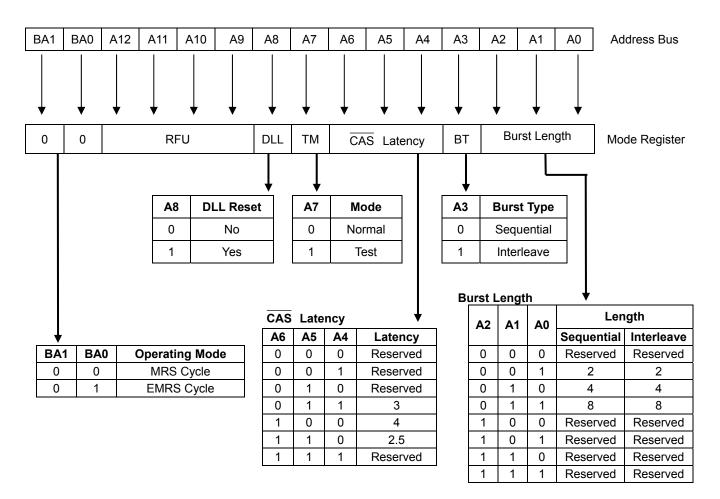

### **Mode Register Definition**

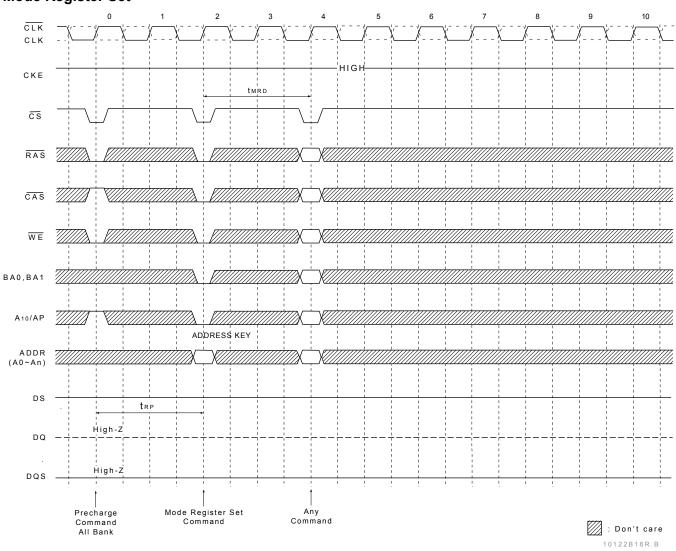

#### Mode Register Set (MRS)

The mode register stores the data for controlling the various operating modes of DDR SDRAM. It programs  $\overrightarrow{CAS}$  latency, addressing mode, burst length, test mode, DLL reset and various vendor specific options to make DDR SDRAM useful for variety of different applications. The default value of the register is not defined, therefore the mode register must be written after EMRS setting for proper DDR SDRAM operation. The mode register is written by asserting low on  $\overrightarrow{CS}$ ,  $\overrightarrow{RAS}$ ,  $\overrightarrow{CAS}$ ,  $\overrightarrow{WE}$  and BA0~BA1 (The DDR SDRAM should be in all bank precharge with CKE already high prior to writing into the mode register). The state of address pins A0~A12 in the same cycle as  $\overrightarrow{CS}$ ,  $\overrightarrow{RAS}$ ,  $\overrightarrow{CAS}$ ,  $\overrightarrow{WE}$  and BA0~BA1 going low is written in the mode register. Two clock cycles are requested to complete the write operation in the mode register. The mode register contents can be changed using the same command and clock cycle requirements during operation as long as all banks are in the idle state. The mode register is divided into various fields depending on functionality. The burst length uses A0~A2, addressing mode uses A3,  $\overrightarrow{CAS}$  latency (read latency from column address) uses A4~A6. A7 is used for test mode. A8 is used for DLL reset. A7 must be set to low for normal MRS operation. Refer to the table for specific codes for various burst length, addressing modes and  $\overrightarrow{CAS}$  latencies.

Note: RFU (Reserved for future use) must stay "0" during MRS cycle.

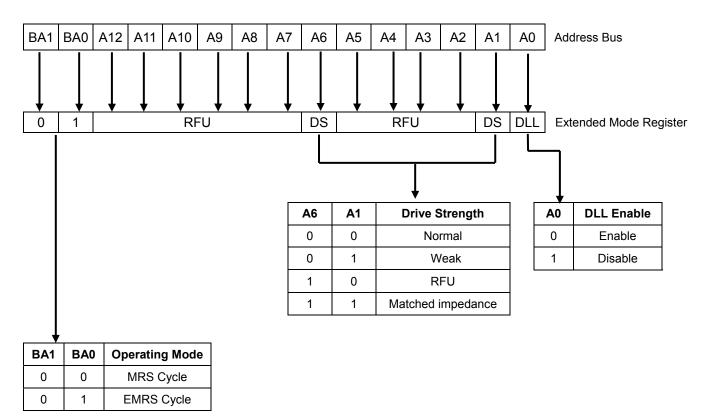

#### Extended Mode Register Set (EMRS)

The extended mode register stores the data enabling or disabling DLL, and selecting output drive strength. The default value of the extended mode register is not defined, therefore the extended mode register must be written after power up for enabling or disabling DLL. The extended mode register is written by asserting low on  $\overline{CS}$ ,  $\overline{RAS}$ ,  $\overline{CAS}$ ,  $\overline{WE}$  and high on BA0 (The DDR SDRAM should be in all bank precharge with CKE already high prior to writing into the extended mode register). The state of address pins A0~A12 and BA0~BA1 in the same cycle as  $\overline{CS}$ ,  $\overline{RAS}$ ,  $\overline{CAS}$  and  $\overline{WE}$  going low is written in the extended mode register contents can be changed using the same command and clock cycle requirements during operation as long as all banks are in the idle state. A0 is used for DLL enable or disable. A1 and A6 are used for selecting output drive strength. "High" on BA0 is used for EMRS. All the other address pins except A0~A1, A6 and BA0 must be set to low for proper EMRS operation. Refer to the table for specific codes.

Note: RFU (Reserved for future use) must stay "0" during EMRS cycle.

|                 | Burst Address Ordering for Burst Length          |                        |                        |  |  |  |  |  |  |  |

|-----------------|--------------------------------------------------|------------------------|------------------------|--|--|--|--|--|--|--|

| Burst<br>Length | Starting<br>Address (A2, A1, A0) Sequential Mode |                        | Interleave Mode        |  |  |  |  |  |  |  |

| 2               | xx0                                              | 0, 1                   | 0, 1                   |  |  |  |  |  |  |  |

| 2               | xx1                                              | 1, 0                   | 1, 0                   |  |  |  |  |  |  |  |

|                 | x00                                              | 0, 1, 2, 3             | 0, 1, 2, 3             |  |  |  |  |  |  |  |

| 4               | x01                                              | 1, 2, 3, 0             | 1, 0, 3, 2             |  |  |  |  |  |  |  |

| 4               | x10                                              | 2, 3, 0, 1             | 2, 3, 0, 1             |  |  |  |  |  |  |  |

|                 | x11                                              | 3, 0, 1, 2             | 3, 2, 1, 0             |  |  |  |  |  |  |  |

|                 | 000                                              | 0, 1, 2, 3, 4, 5, 6, 7 | 0, 1, 2, 3, 4, 5, 6, 7 |  |  |  |  |  |  |  |

|                 | 001                                              | 1, 2, 3, 4, 5, 6, 7, 0 | 1, 0, 3, 2, 5, 4, 7, 6 |  |  |  |  |  |  |  |

|                 | 010                                              | 2, 3, 4, 5, 6, 7, 0, 1 | 2, 3, 0, 1, 6, 7, 4, 5 |  |  |  |  |  |  |  |

| 8               | 011                                              | 3, 4, 5, 6, 7, 0, 1, 2 | 3, 2, 1, 0, 7, 6, 5, 4 |  |  |  |  |  |  |  |

| 0               | 100                                              | 4, 5, 6, 7, 0, 1, 2, 3 | 4, 5, 6, 7, 0, 1, 2, 3 |  |  |  |  |  |  |  |

|                 | 101                                              | 5, 6, 7, 0, 1, 2, 3, 4 | 5, 4, 7, 6, 1, 0, 3, 2 |  |  |  |  |  |  |  |

|                 | 110                                              | 6, 7, 0, 1, 2, 3, 4, 5 | 6, 7, 4, 5, 2, 3, 0, 1 |  |  |  |  |  |  |  |

|                 | 111                                              | 7, 0, 1, 2, 3, 4, 5, 6 | 7, 6, 5, 4, 3, 2, 1, 0 |  |  |  |  |  |  |  |

#### DLL Enable / Disable

The DLL must be enabled for normal operation. DLL enable is required during power-up initialization, and upon returning to normal operation after having disabled the DLL for the purpose of debug or evaluation (upon exiting Self Refresh Mode, the DLL is enabled automatically). Any time the DLL is enabled, 200 clock cycles must occur before a READ command can be issued.

#### **Output Drive Strength**

The normal drive strength for all outputs is specified to be SSTL\_2, Class II. The device also support reduced drive strength options, intended for lighter load and/or point-to-point environments.

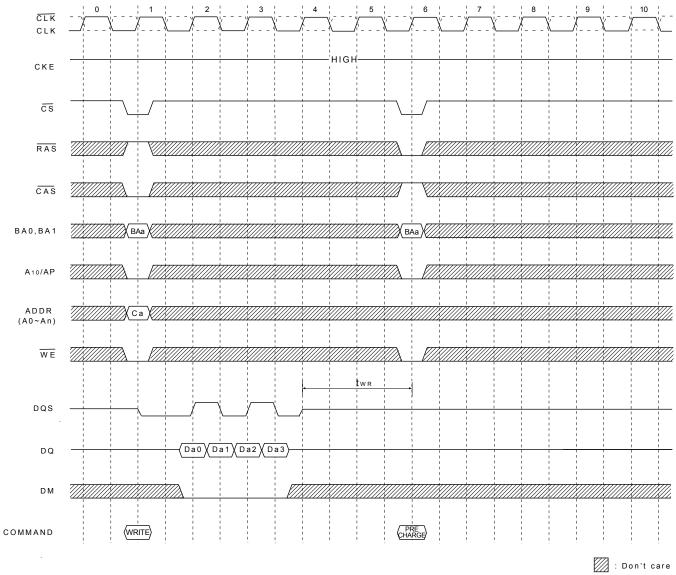

#### Precharge

The precharge command is used to precharge or close a bank that has activated. The precharge command is issued when  $\overline{\text{CS}}$ ,

$\overline{RAS}$  and  $\overline{WE}$  are low and  $\overline{CAS}$  is high at the rising edge of the clock. The precharge command can be used to precharge each bank respectively or all banks simultaneously. The bank select addresses (BA0, BA1) are used to define which bank is precharged when the command is initiated. For write cycle, t<sub>WR</sub>(min) must be satisfied until the precharge command can be issued. After t<sub>RP</sub> from the precharge, an active command to the same bank can be initiated.

| A10/AP | A10/AP BA1 |   | Precharge   |

|--------|------------|---|-------------|

| 0      | 0          | 0 | Bank A Only |

| 0      | 0          | 1 | Bank B Only |

| 0      | 1          | 0 | Bank C Only |

| 0      | 1          | 1 | Bank D Only |

| 1      | Х          | Х | All Banks   |

#### Burst Selection for Precharge by bank address bits

### No Operation & Device Deselect

The device should be deselected by deactivating the  $\overline{CS}$  signal. In this mode DDR SDRAM should ignore all the control inputs. The DDR SDRAMs are put in NOP mode when  $\overline{CS}$  is active and by deactivating  $\overline{RAS}$ ,  $\overline{CAS}$  and  $\overline{WE}$ . For both Deselect and NOP the device should finish the current operation when this command is issued.

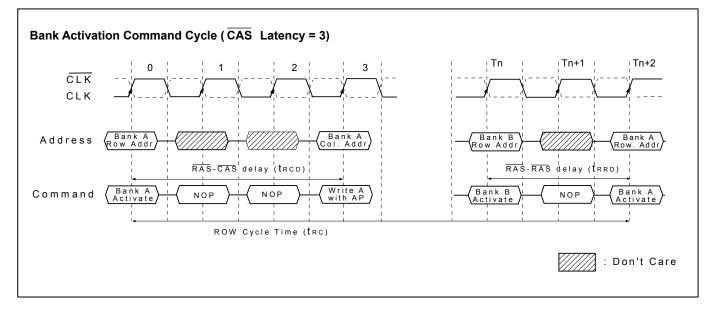

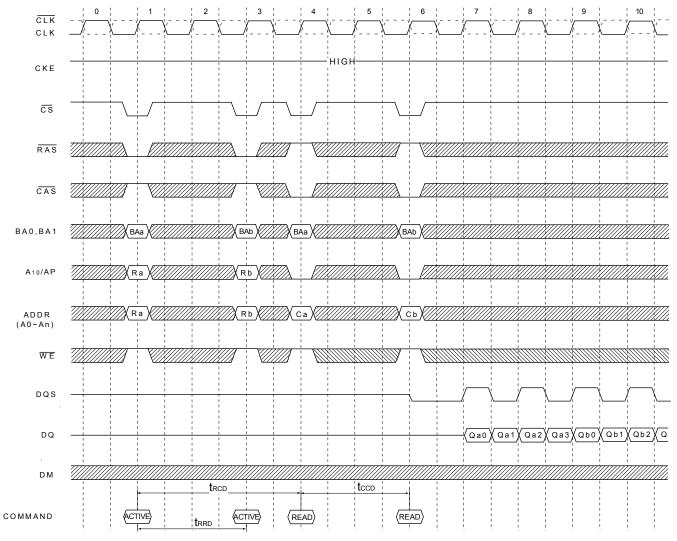

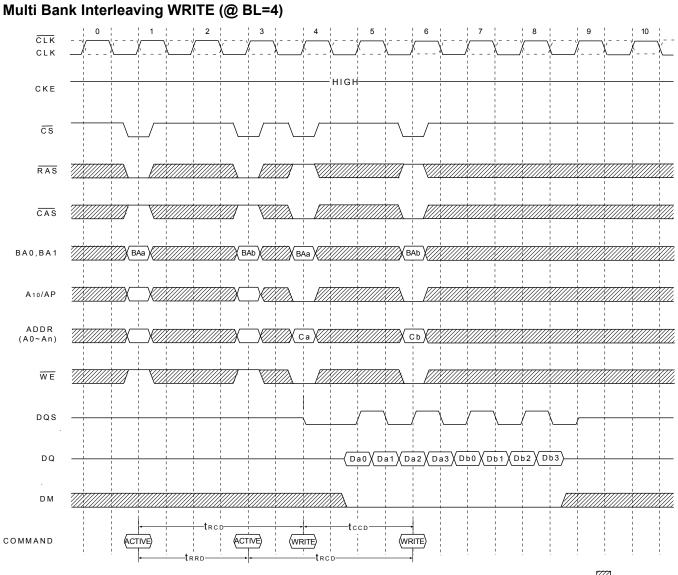

### Bank / Row Active

The Bank Activation command is issued by holding  $\overline{CAS}$  and  $\overline{WE}$  high with  $\overline{CS}$  and  $\overline{RAS}$  low at the rising edge of the clock (CLK). The DDR SDRAM has four independent banks, so Bank Select addresses (BA0, BA1) are required. The Bank Activation command must be applied before any Read or Write operation is executed. The Bank Activation command to the first Read or Write command must meet or exceed the minimum of  $\overline{RAS}$  to  $\overline{CAS}$  delay time (t<sub>RCD</sub> min). Once a bank has been activated, it must be precharged before another Bank Activation command can be applied to the same bank. The minimum time interval between interleaved Bank Activation command (Bank A to Bank B and vice versa) is the Bank to Bank delay time (t<sub>RRD</sub> min).

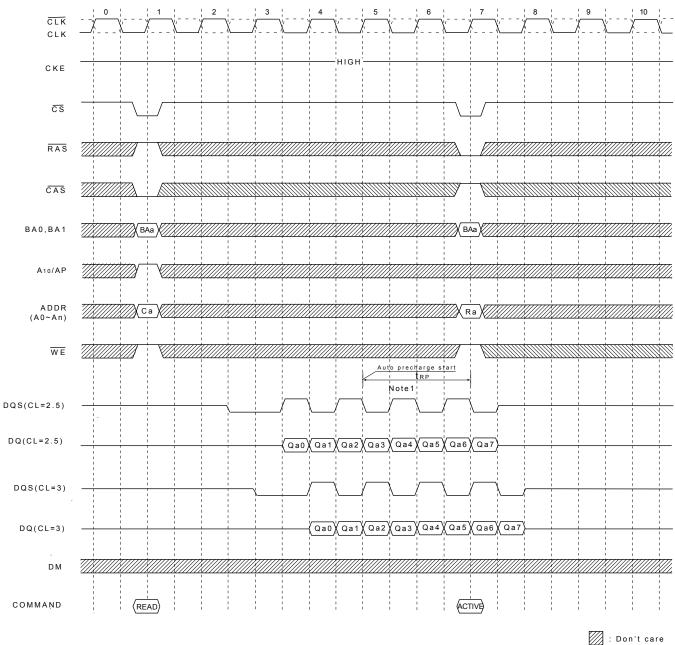

#### Read

This command is used after the row activate command to initiate the burst read of data. The read command is initiated by activating  $\overline{CS}$ ,  $\overline{RAS}$ ,  $\overline{CAS}$ , and deasserting  $\overline{WE}$  at the same clock rising edge as described in the command truth table. The length of the burst and the CAS latency time will be determined by the values programmed during the MRS command.

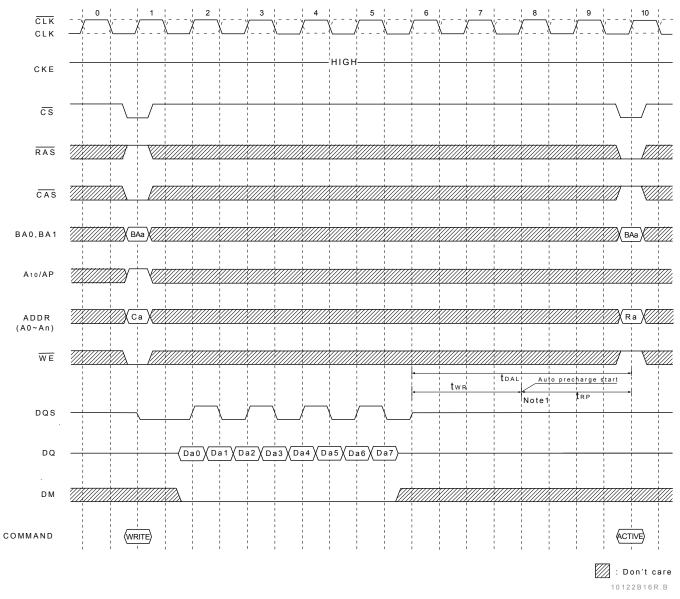

#### Write

This command is used after the row activate command to initiate the burst write of data. The write command is initiated by activating  $\overline{CS}$ ,  $\overline{RAS}$ ,  $\overline{CAS}$ , and  $\overline{WE}$  at the same clock rising edge as describe in the command truth table. The length of the burst will be determined by the values programmed during the MRS command.

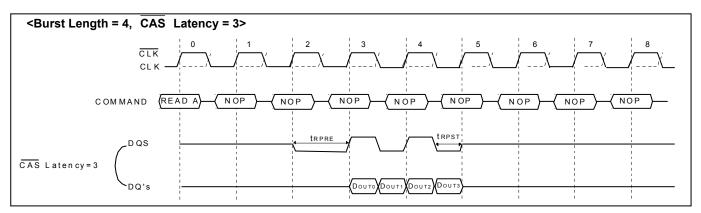

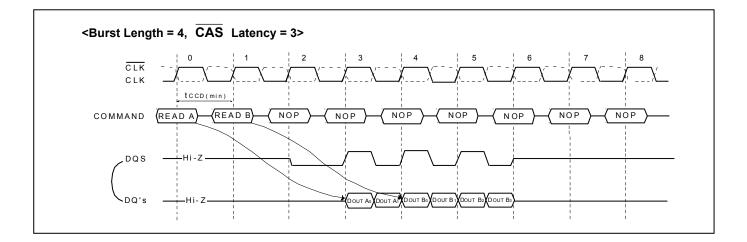

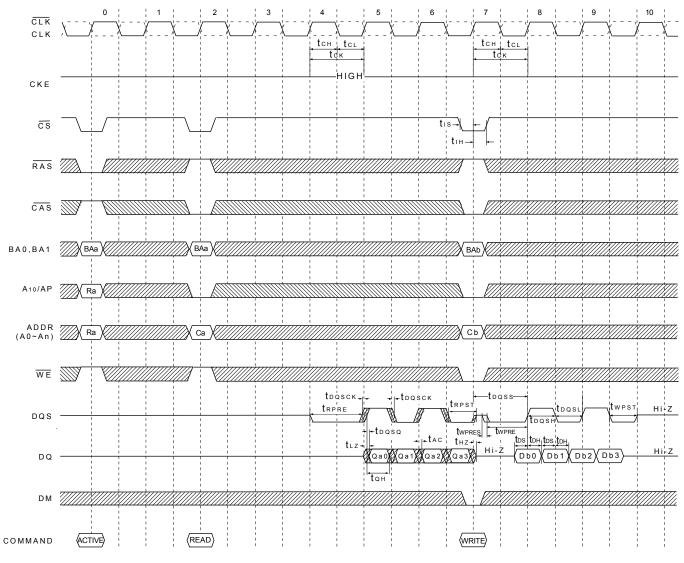

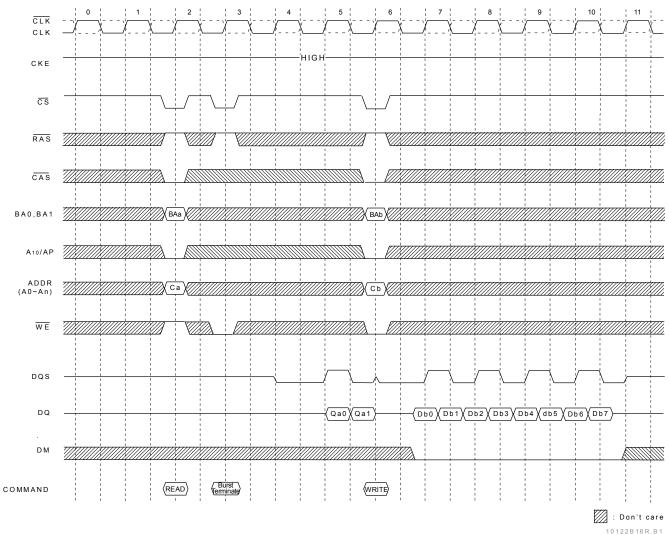

#### **Burst Read Operation**

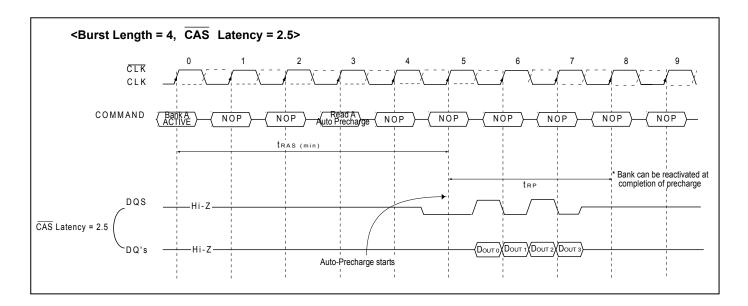

Burst Read operation in DDR SDRAM is in the same manner as the current SDRAM such that the Burst read command is issued by asserting  $\overline{CS}$  and  $\overline{CAS}$  low while holding  $\overline{RAS}$  and  $\overline{WE}$  high at the rising edge of the clock (CLK) after t<sub>RCD</sub> from the bank activation. The address inputs determine the starting address for the Burst. The Mode Register sets type of burst (Sequential or interleave) and burst length (2, 4, 8). The first output data is available after the  $\overline{CAS}$  Latency from the READ command, and the consecutive data are presented on the falling and rising edge of Data Strobe (DQS) adopted by DDR SDRAM until the burst length is completed.

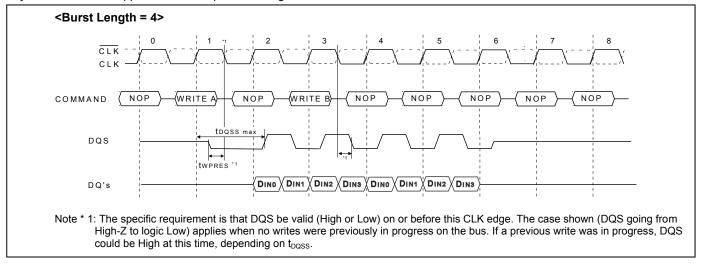

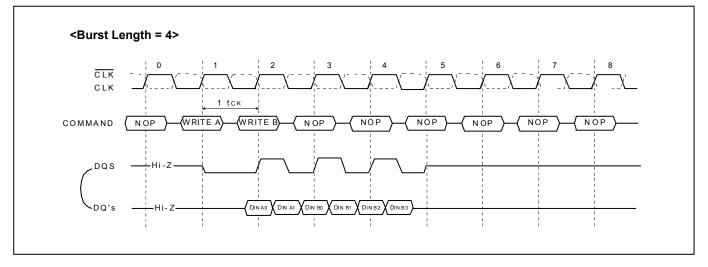

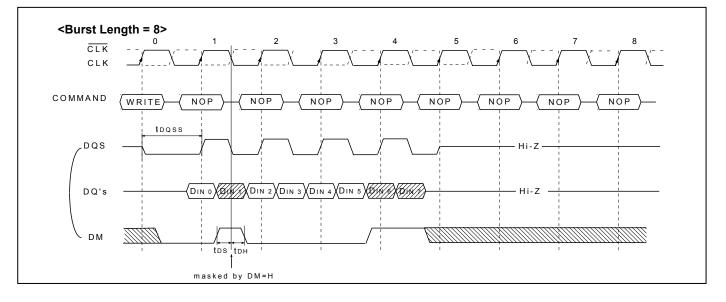

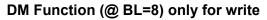

### **Burst Write Operation**

The Burst Write command is issued by having  $\overline{CS}$ ,  $\overline{CAS}$  and  $\overline{WE}$  low while holding  $\overline{RAS}$  high at the rising edge of the clock (CLK). The address inputs determine the starting column address. There is no write latency relative to DQS required for burst write cycle. The first data of a burst write cycle must be applied on the DQ pins t<sub>DS</sub> prior to data strobe edge enabled after t<sub>DQSS</sub> from the rising edge of the clock (CLK) that the write command is issued. The remaining data inputs must be supplied on each subsequent falling and rising edge of Data Strobe until the burst length is completed. When the burst has been finished, any additional data supplied to the DQ pins will be ignored.

ChamptechTechnology Inc.

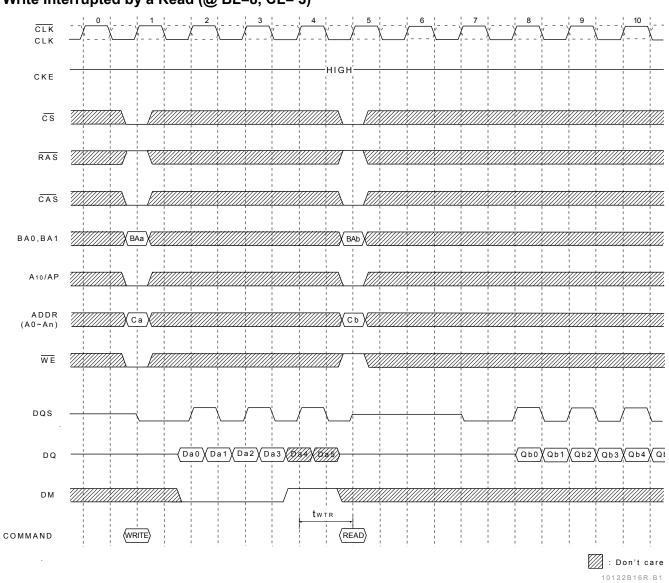

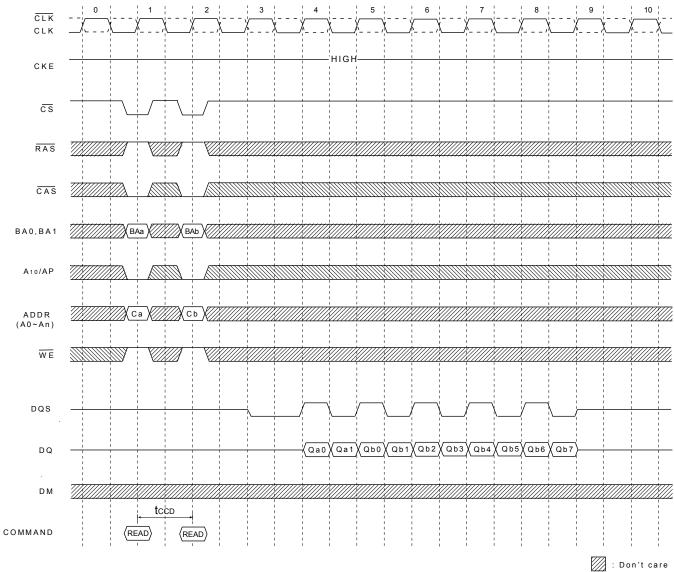

#### Read Interrupted by a Read

A Burst Read can be interrupted before completion of the burst by new Read command of any bank. When the previous burst is interrupted, the remaining addresses are overridden by the new address with the full burst length. The data from the first Read command continues to appear on the outputs until the  $\overline{CAS}$  latency from the interrupting Read command is satisfied. At this point the data from the interrupting Read command appears. Read to Read interval is  $t_{CCD}(min)$ .

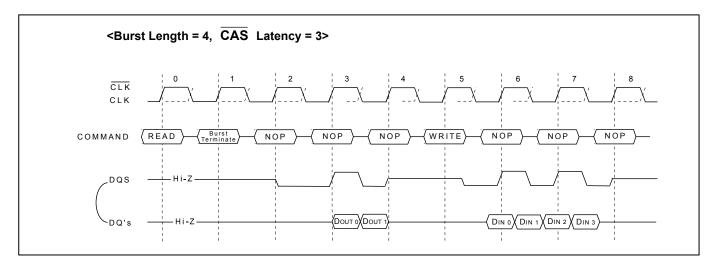

#### Read Interrupted by a Write & Burst Terminate

To interrupt a burst read with a write command, Burst Terminate command must be asserted to avoid data contention on the I/O bus by placing the DQ's (Output drivers) in a high impedance state. To insure the DQ's are tri-stated one cycle before the beginning the write operation, Burt stop command must be applied at least RU(CL) clocks [RU mean round up to the nearest integer] before the Write command.

The following functionality establishes how a Write command may interrupt a Read burst.

- For Write commands interrupting a Read burst, a Burst Terminate command is required to stop the read burst and tristate the DQ bus prior to valid input write data. Once the Burst Terminate command has been issued, the minimum delay to a Write command = RU(CL) [CL is the CAS Latency and RU means round up to the nearest integer].

- 2. It is illegal for a Write and Burst Terminate command to interrupt a Read with auto precharge command.

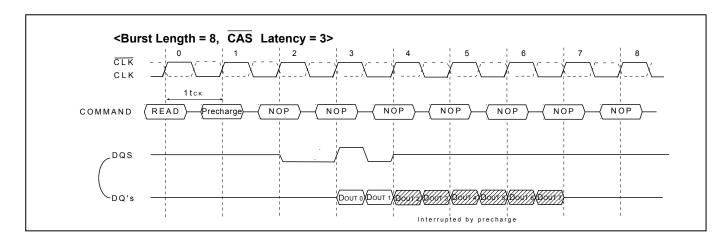

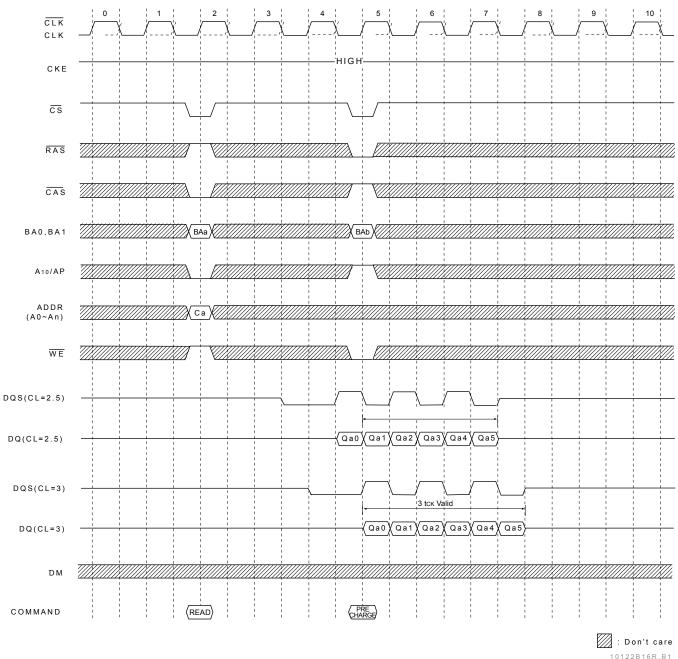

#### Read Interrupted by a Precharge

A Burst Read operation can be interrupted by precharge of the same bank. The minimum 1 clock is required for the read to precharge intervals. A precharge command to output disable latency is equivalent to the  $\overline{CAS}$  latency.

When a burst Read command is issued to a DDR SDRAM, a Precharge command may be issued to the same bank before the Read burst is complete. The following functionality determines when a Precharge command may be given during a Read burst and when a new Bank Activate command may be issued to the same bank.

- 1. For the earliest possible Precharge command without interrupting a Read burst, the Precharge command may be given on the rising clock edge which is CL clock cycles before the end of the Read burst where CL is the  $\overline{CAS}$  Latency. A new Bank Activate command may be issued to the same bank after t<sub>RP</sub> (RAS precharge time).

- 2. When a Precharge command interrupts a Read burst operation, the Precharge command may be given on the rising clock edge which is CL clock cycles before the last data from the interrupted Read burst where CL is the  $\overline{CAS}$  Latency. Once the last data word has been output, the output buffers are tristated. A new Bank Activate command may be issued to the same bank after  $t_{RP}$ .

- 3. For a Read with auto precharge command, a new Bank Activate command may be issued to the same bank after  $t_{RP}$  where  $t_{RP}$  begins on the rising clock edge which is CL clock cycles before the end of the Read burst where CL is the  $\overline{CAS}$  Latency. During Read with auto precharge, the initiation of the internal precharge occurs at the same time as the earliest possible external Precharge command would initiate a precharge operation without interrupting the Read burst as described in 1 above.

- 4. For all cases above, t<sub>RP</sub> is an analog delay that needs to be converted into clock cycles. The number of clock cycles between a Precharge command and a new Bank Activate command to the same bank equals t<sub>RP</sub> / t<sub>CK</sub> (where t<sub>CK</sub> is the clock cycle time) with the result rounded up to the nearest integer number of clock cycles.

In all cases, a Precharge operation cannot be initiated unless  $t_{RAS}$  (min) [minimum Bank Activate to Precharge time] has been satisfied. This includes Read with auto precharge commands where  $t_{RAS}$  (min) must still be satisfied such that a Read with auto precharge command has the same timing as a Read command followed by the earliest possible Precharge command which does not interrupt the burst.

### Write Interrupted by a Write

A Burst Write can be interrupted before completion of the burst by a new Write command, with the only restriction that the interval that separates the commands must be at least one clock cycle. When the previous burst is interrupted, the remaining addresses are overridden by the new address and data will be written into the device until the programmed burst length is satisfied.

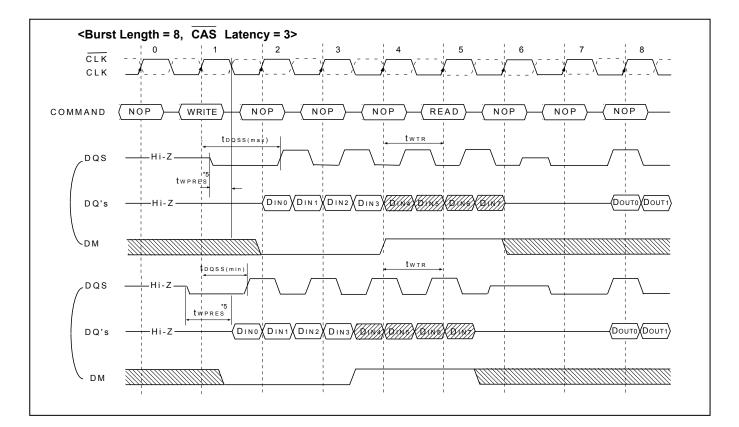

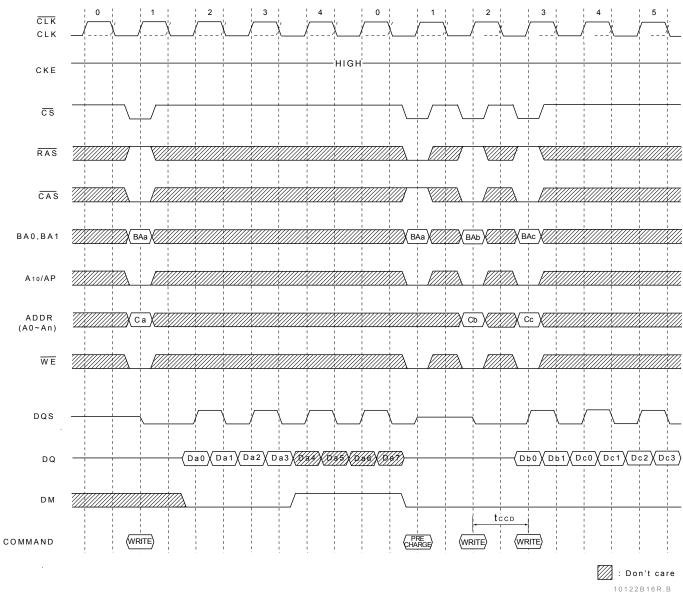

#### Write Interrupted by a Read & DM

A burst write can be interrupted by a read command of any bank. The DQ's must be in the high impedance state at least one clock cycle before the interrupting read data appear on the outputs to avoid data contention. When the read command is registered, any residual data from the burst write cycle must be masked by DM. The delay from the last data to read command  $(t_{WTR})$  is required to avoid the data contention DRAM inside. Data that are presented on the DQ pins before the read command is initiated will actually be written to the memory. Read command interrupting write can not be issued at the next clock edge of that of write command.

The following functionality established how a Read command may interrupt a Write burst and which input data is not written into the memory.

- 1. For Read commands interrupting a Write burst, the minimum Write to Read command delay is 2 clock cycles. The case where the Write to Read delay is 1 clock cycle is disallowed.

- 2. For read commands interrupting a Write burst, the DM pin must be used to mask the input data words which immediately precede the interrupting Read operation and the input data word which immediately follows the interrupting Read operation.

- 3. For all cases of a Read interrupting a Write, the DQ and DQS buses must be released by the driving chip (i.e., the memory controller) in time to allow the buses to turn around before the SDRAM drives them during a read operation.

- 4. If input Write data is masked by the Read command, the DQS inputs are ignored by the DDR SDRAM.

- 5. Refer to "Burst write operation"

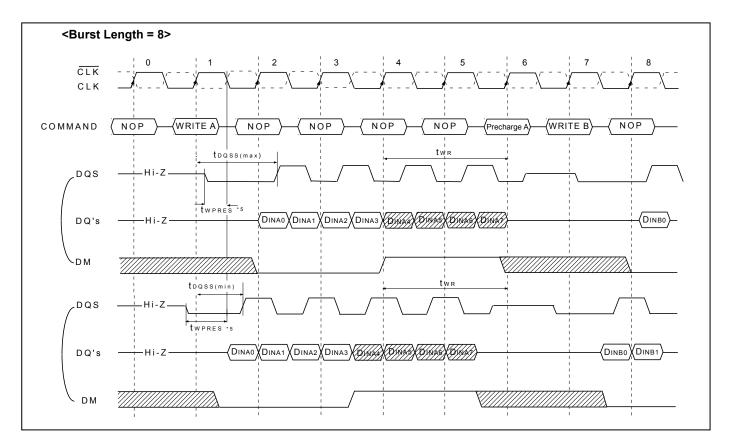

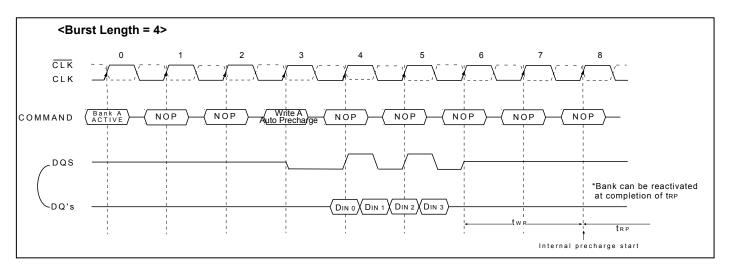

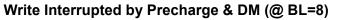

#### Write Interrupted by a Precharge & DM

A burst write operation can be interrupted before completion of the burst by a precharge of the same bank. Random column access is allowed. A write recovery time ( $t_{WR}$ ) is required from the last data to precharge command. When precharge command is asserted, any residual data from the burst write cycle must be masked by DM.

Precharge timing for Write operations in DRAMs requires enough time to allow "write recovery" which is the time required by a DRAM core to properly store a full "0" or "1" level before a Precharge operation. For DDR SDRAM, a timing parameter,  $t_{WR}$ , is used to indicate the required of time between the last valid write operation and a Precharge command to the same bank.

$t_{WR}$  starts on the rising clock edge after the last possible DQS edge that strobed in the last valid and ends on the rising clock edge that strobes in the precharge command.

- 1. For the earliest possible Precharge command following a Write burst without interrupting the burst, the minimum time for write recovery is defined by  $t_{WR}$ .

- 2. When a precharge command interrupts a Write burst operation, the data mask pin, DM, is used to mask input data during the time between the last valid write data and the rising clock edge in which the Precharge command is given. During this time, the DQS input is still required to strobe in the state of DM. The minimum time for write recovery is defined by t<sub>WR</sub>.

- 3. For a Write with auto precharge command, a new Bank Activate command may be issued to the same bank after  $t_{WR} + t_{RP}$  where  $t_{WR} + t_{RP}$  starts on the falling DQS edge that strobed in the last valid data and ends on the rising clock edge that strobes in the Bank Activate commands. During write with auto precharge, the initiation of the internal precharge occurs at the same time as the earliest possible external Precharge command without interrupting the Write burst as described in 1 above.

- 4. In all cases, a Precharge operation cannot be initiated unless t<sub>RAS</sub>(min) [minimum Bank Activate to Precharge time] has been satisfied. This includes Write with auto precharge commands where t<sub>RAS</sub>(min) must still be satisfied such that a Write with auto precharge command has the same timing as a Write command followed by the earliest possible Precharge command which does not interrupt the burst.

- 5. Refer to "Burst write operation"

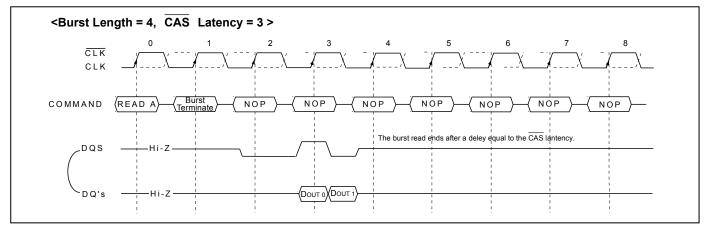

#### **Burst Terminate**

The burst terminate command is initiated by having  $\overrightarrow{RAS}$  and  $\overrightarrow{CAS}$  high with  $\overrightarrow{CS}$  and  $\overrightarrow{WE}$  low at the rising edge of the clock (CLK). The burst terminate command has the fewest restrictions making it the easiest method to use when terminating a burst read operation before it has been completed. When the burst terminate command is issued during a burst read cycle, the pair of data and DQS (Data Strobe) go to a high impedance state after a delay which is equal to the  $\overrightarrow{CAS}$  latency set in the mode register. The burst terminate command, however, is not supported during a write burst operation.

The Burst Terminate command is a mandatory feature for DDR SDRAMs. The following functionality is required.

- 1. The BST command may only be issued on the rising edge of the input clock, CLK.

- 2. BST is only a valid command during Read burst.

- 3. BST during a Write burst is undefined and shall not be used.

- 4. BST applies to all burst lengths.

- 5. BST is an undefined command during Read with auto precharge and shall not be used.

- 6. When terminating a burst Read command, the BST command must be issued  $L_{BST}$  ("BST Latency") clock cycles before the clock edge at which the output buffers are tristated, where  $L_{BST}$  equals the  $\overline{CAS}$  latency for read operations.

- 7. When the burst terminates, the DQ and DQS pins are tristated.

The BST command is not byte controllable and applies to all bits in the DQ data word and the (all) DQS pin(s).

#### DM masking

The DDR SDRAM has a data mask function that can be used in conjunction with data write cycle. Not read cycle. When the data mask is activated (DM high) during write operation, DDR SDRAM does not accept the corresponding data. (DM to data-mask latency is zero) DM must be issued at the rising or falling edge of data strobe.

ChamptechTechnology Inc.

### **Read With Auto Precharge**

If a read with auto precharge command is initiated, the DDR SDRAM automatically enters the precharge operation BL/2 clock later from a read with auto precharge command when  $t_{RAS}$  (min) is satisfied. If not, the start point of precharge operation will be delayed until  $t_{RAS}$  (min) is satisfied. Once the precharge operation has started the bank cannot be reactivated and the new command can not be asserted until the precharge time ( $t_{RP}$ ) has been satisfied.

When the Read with Auto Precharge command is issued, new command can be asserted at 4, 5 and 6 respectively as follow.

| Asserted                   | F            | or the same ban | k       | For the different bank |       |       |  |

|----------------------------|--------------|-----------------|---------|------------------------|-------|-------|--|

| Command                    | 4            | 5               | 6       | 4                      | 5     | 6     |  |

| READ                       | READ         | Illegal         | lllegal | Legal                  | Legal | Legal |  |

| READ with AP <sup>*1</sup> | READ with AP | Illegal         | Illegal | Legal                  | Legal | Legal |  |

| Active                     | Illegal      | Illegal         | Illegal | Legal                  | Legal | Legal |  |

| Precharge                  | Legal        | Legal           | Illegal | Legal                  | Legal | Legal |  |

Note 1: AP = Auto Precharge

#### Write with Auto Precharge

If A10 is high when write command is issued, the write with auto-precharge function is performed. Any new command to the same bank should not be issued until the internal precharge is completed. The internal precharge begins at the rising edge of the CLK with the  $t_{WR}$  delay after the last data-in.

At burst read / write with auto precharge, CAS interrupt of the same bank is illegal.

| Asserted                    |                  | For                        | the same b             | ank             |         | For the different bank |         |         |       |       |

|-----------------------------|------------------|----------------------------|------------------------|-----------------|---------|------------------------|---------|---------|-------|-------|

| Command                     | 4                | 5                          | 6                      | 7               | 8       | 4                      | 5       | 6       | 7     | 8     |

| WRITE                       | WRITE            | WRITE                      | Illegal                | Illegal         | Illegal | Legal                  | Legal   | Legal   | Legal | Legal |

| WRITE with AP <sup>*1</sup> | WRITE<br>with AP | WRITE<br>with AP           | Illegal                | Illegal         | Illegal | Legal                  | Legal   | Legal   | Legal | Legal |

| READ                        | Illegal          | READ +<br>DM <sup>*2</sup> | READ+<br>DM            | READ            | Illegal | Illegal                | lllegal | Illegal | Legal | Legal |

| READ with AP                | Illegal          | READ<br>with AP+<br>DM     | READ<br>with AP+<br>DM | READ<br>with AP | Illegal | Illegal                | Illegal | Illegal | Legal | Legal |

| Active                      | Illegal          | Illegal                    | Illegal                | Illegal         | Illegal | Legal                  | Legal   | Legal   | Legal | Legal |

| Precharge                   | lllegal          | Illegal                    | Illegal                | Illegal         | Illegal | Legal                  | Legal   | Legal   | Legal | Legal |

Note: 1. AP = Auto Precharge

2. DM: Refer to "Write Interrupted by a Read & DM"

### Auto Refresh & Self Refresh

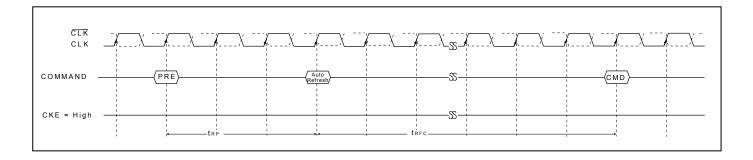

#### Auto Refresh

An auto refresh command is issued by having  $\overline{CS}$ ,  $\overline{RAS}$  and  $\overline{CAS}$  held low with CKE and  $\overline{WE}$  high at the rising edge of the clock (CLK). All banks must be precharged and idle for  $t_{RP}(min)$  before the auto refresh command is applied. No control of the external address pins is requires once this cycle has started because of the internal address counter. When the refresh cycle has completed, all banks will be in the idle state. A delay between the auto refresh command and the next activate command or subsequent auto refresh command must be greater than or equal to the  $t_{RFC}(min)$ . A maximum of eight consecutive AUTO REFRESH commands (with  $t_{RFC}(min)$ ) can be posted to any given DDR SDRAM

A maximum of eight consecutive AUTO REFRESH commands (with  $t_{RFC}(min)$ ) can be posted to any given DDR SDRAM meaning that the maximum absolute interval between any AUTO REFRESH command and the next AUTO REFRESH command is 8 x  $t_{REFI}$ .

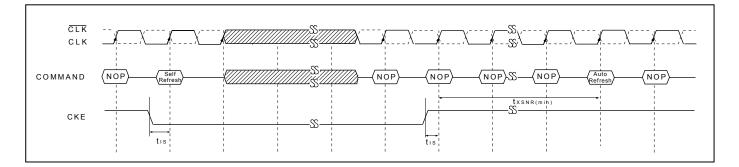

#### Self Refresh

A self refresh command is defines by having  $\overline{CS}$ ,  $\overline{RAS}$ ,  $\overline{CAS}$  and CKE held low with  $\overline{WE}$  high at the rising edge of the clock (CLK). Once the self refresh command is initiated, CKE must be held low to keep the device in self refresh mode. During the self refresh operation, all inputs except CKE are ignored. Since CKE is an SSTL\_2 input, V<sub>REF</sub> must be maintained during self refresh. The clock is internally disabled during self refresh operation to reduce power consumption. The self refresh is exited by supplying stable clock input before returning CKE high, asserting deselect or NOP command and then asserting CKE high for longer than t<sub>XSRD</sub> for locking of DLL.

Note: After self refresh exit, input an auto refresh command immediately.

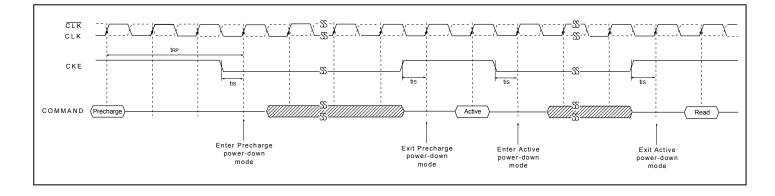

#### **Power down**

Power down is entered when CKE is registered Low (no accesses can be in progress). If power down occurs when all banks are idle, this mode is referred to as precharge power-down; if power down occurs when there is a row active in any bank, this mode is referred to as active power-down.

Entering power down deactivates the input and output buffers, excluding CLK,  $\overline{\text{CLK}}$  and CKE. In power down mode, CKE Low must be maintained, and all other input signals are "Don't Care". The minimum power down duration is at least 1 t<sub>CK</sub> + t<sub>IS</sub>. However, power down duration is limited by the refresh requirements of the device.

The power down state is synchronously exited when CKE is registered High (along with a NOP or DESELECT command). A valid command may be applied 1  $t_{CK}$  +  $t_{IS}$  after exit from power down.

# **Functional Truth Table**

# Truth Table – CKE <sup>[Note 1~4, 6]</sup>

| CKE n-1 | CKE n | Current State                  | COMMAND n       | ACTION n                   | NOTE |  |  |

|---------|-------|--------------------------------|-----------------|----------------------------|------|--|--|

| L       | L     | Power Down                     | Х               | Maintain Power Down        |      |  |  |